Project: ISOLDE: customizable Instruction Sets and Open Leveraged Designs of Embedded riscv processors

Reference number: 101112274

Project duration: 01.05.2023 - 30.04.2026

Work Package: WP1: Requirements and Specifications

Deliverable D1.2

# Title Requirements and specifications on architecture, hardware and software modules and IPs

| Type of deliverable:             | Report                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Deadline:                        | 31.10.2023                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Creation date:                   | 12.09.2023                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Dissemination Level:<br>Authors: | PU - Public<br>Antonio Sciarappa, LDO                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                  | Rafael Tornero, UPV<br>Daniel Gracia Pérez, TRT<br>Stefan Wallentowitz, HM<br>Georg Pacher, NXP-AT<br>Erik Kraft, NXP-AT<br>Samu Ardaya-Lieb, CONS<br>Holger Blasum, SYSGO<br>André Sintzoff, TDIS<br>Nils Wessman, GSL<br>Andrea Galimberti, POLIMI<br>William Fornaciari, POLIMI<br>William Fornaciari, POLIMI<br>Davide Zoni, POLIMI<br>Federico Reghenzani, POLIMI<br>Giovanni Agosta, POLIMI<br>Alessio Burrello, POLITO<br>Daniele Jahier Pagliari, POLITO<br>Jan Kaštil, CODA |

|                     | Václav Šimek, BUT<br>Petr Fajmon, NXP-CZ<br>Behnam Razi Perjikolaei, OFFIS<br>Dominik Riemer, BYK<br>Esther Soriano, FEN<br>Christopher Blochwitz, UZL<br>Jaume Abella, BSC<br>Juan Antonio Rodríguez Gracia, BSC<br>Xavier Carril Gil, BSC<br>A. Wilson, D. Gigena-Ivanovich, W. Krenn, M. Freiberger, SAL<br>Sebastian Reiter, FZI<br>Mihai Munteanu, Alexandru Drimbarean, Honorius Galmeanu, XPERI<br>Paolo Serri, TASI<br>Matteo Perotti, ETHZ<br>Simona Costinescu NXP-RO<br>Calin Bira UNSTPB                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Involved partners:  | Leonardo S.p.A. (LDO)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| invoiveu partifeis: | Universitat Politècnica de València (UPV)<br>Thales Research & Technology (TRT)<br>Hochschule München University of Applied Sciences (HM)<br>NXP Semiconductors Austria GmbH & Co KG (NXP-AT)<br>NXP Semiconductors Czech Republic, s.r.o. (NXP-CZ)<br>SYSGO GmbH (SYSGO)<br>Consolinno Energy GmbH (CONS)<br>Thales DIS France SAS (TDIS)<br>Frontgrde Gaisler (GSL)<br>Politecnico di Milano (POLIMI)<br>Politecnico of Turin (POLITO)<br>Codasip SRO (CODA)<br>Bytefabrik.AI GmbH (BYK)<br>OFFIS e.V. (OFFIS)<br>Fent Innovative Software Solutions S.L. (FEN)<br>University of Lübeck (UZL)<br>Barcelona Supercomputing Center (BSC)<br>Silicon Austria Labs GmbH (SAL)<br>Xperi FotoNation SRL (XPERI)<br>FZI Forschungszentrum Informatik (FZI)<br>Brno University of Technology (BUT)<br>Thales Alenia Space Italia S.p.A. (TASI)<br>Eidgenössische Technische Hochschule Zürich (ETHZ)<br>NXP Semiconductors Romania (NXP-RO) |

POLITEHNICA București National University for Science and Technology (UNSTPB)

Responsible partner:

Antonio Sciarappa, LDO, antonio.sciarappa@leonardo.com

# **Change Records**

| REV | DATE       | § CHANGE RECORDS       | ANGE RECORDS AUTHOR                                |  |

|-----|------------|------------------------|----------------------------------------------------|--|

| 0.1 | 12/09/2023 | Initial draft template | Antonio Sciarappa                                  |  |

| 0.2 | 19/10/2023 | First version          | All partners                                       |  |

| 0.3 | 27/10/2023 | Second version         | All partners                                       |  |

| 0.4 | 03/11/2023 | Review                 | Aurel Gontean, Danut Rotar, Stefan<br>Wallentowitz |  |

| 0.5 | 10/11/2023 | Comments solved        | Antonio Sciarappa, all partners                    |  |

| 0.6 | 24/11/2023 | Deliverable cleaned    | Antonio Sciarappa                                  |  |

|     |            |                        |                                                    |  |

|     |            |                        |                                                    |  |

|     |            |                        |                                                    |  |

|     |            |                        |                                                    |  |

|     |            |                        |                                                    |  |

|     |            |                        |                                                    |  |

|     |            |                        |                                                    |  |

| Ex   | ecutive Summary                                                                     | 8            |

|------|-------------------------------------------------------------------------------------|--------------|

| 1 lı | ntroduction                                                                         | 9            |

| 1    | .1 Definitions and Acronyms                                                         | 10           |

| 2    | Cores, interfaces, peripherals & NoCs                                               | 11           |

| 2    | 2.1 Processors                                                                      | 11           |

|      | 2.1.1 NOEL-V processor extensions                                                   | 11           |

|      | 2.1.2 CVA6 processor extensions                                                     | 13           |

|      | 2.1.3 CV32E40X processor extensions                                                 | 14           |

|      | 2.1.4 Testing Design Parameters for CVA6                                            | 15           |

|      | 2.1.5 Analysis Framework (IFX WI2.1.1-2.1.3)                                        | 16           |

| 2    | 2.2 Peripheral and interconnect                                                     | 17           |

|      | 2.2.1 Context-Aware Bus (CA-BUS)                                                    | 17           |

|      | 2.2.2 Wormhole NoC                                                                  | 19           |

|      | 2.2.3 AXI Sniffer                                                                   | 20           |

|      | 2.2.4 AHB Crossbar (IFX WI2.2.1-2.2.3)                                              | 21           |

|      | 2.2.5 AHB/APB Interrupt Controller (IFX WI2.2.4-2.2.5)                              | 22           |

|      | 2.2.6 AHB/APB Timer (IFX WI2.2.6-2.2.7)                                             | 23           |

|      | 2.2.7 GRLIB IP library                                                              | 24           |

| 2    | 2.3 Common extension interfaces                                                     | 25           |

|      | 2.3.1 Context-Aware CORE Extensions (CA-CORE)                                       | 25           |

|      | 2.3.2 Memory bank interface                                                         | 27           |

|      | 2.3.3 Extension interface for NOEL-V                                                | 29           |

|      | 2.3.4 Extension interface for CVA6                                                  | 30           |

|      | 2.3.5 Extension interface between CVA6 and Vector accelerator                       | 31           |

| 2    | 2.4 SW interfaces to general purpose cores                                          | 32           |

|      | 2.4.1 XNG NOEL-V BSP update to new standards                                        | 32           |

|      | 2.4.2 CVA-6 multicore experiments and analysis                                      | 34           |

|      | 2.4.3 SW Abstraction Layer for RISC-V Processors (IFX WI 2.4.1 2.4.3)               | 35           |

|      | 2.4.4 NOEL-V software tools                                                         | 36           |

| 3    | Accelerators and extensions                                                         | 37           |

| 3    | 3.1 Safety and Security modules                                                     | 37           |

|      | 3.1.1 Safety-related Traffic Injector (SafeTI)                                      | 37           |

|      | 3.1.2 Context-Aware PMC Interface (CA-PMC-IF)                                       | 39           |

|      | 3.1.3 Forward-Edge Control Flow Integrity Unit (FCFI)                               | 40           |

|      | 3.1.5 Cryptographically Tagged Memory Unit (CTM)                                    | 42           |

|      | 3.1.6 Enclave Memory Isolation Unit (EMI)                                           | 43           |

|      | 3.1.7 Lightweight Tweakable Inline Memory Encryption Engine (IEE)                   | 44           |

|      | 3.1.8 Memory subsystem support for Bytecode VMs                                     | 45           |

|      | 3.1.9 Safety Island – Interface Definition                                          | 46           |

|      | 3.1.10 Root-of-Trust unit design and interface with RISC-V Host processor (Tit      | •            |

| -    | 3.1.11 Safety Control (IFX WI3.1.1-3.1.4)                                           | 48           |

| -    | B.2 Accelerator infrastructure, memories, arithmetic units, inter<br>virtualization | faces and 49 |

| v    | 3.2.1 Floating-Point Unit (FPU) for RISC-V                                          | <b>49</b>    |

|      |                                                                                     |              |

| D1   | .2 ISOLDE - confidential                                                            | 31.10.2023   |

| 3.2.2 FPU for mixed-precision computing (FPMIX)                                                            | 50                 |

|------------------------------------------------------------------------------------------------------------|--------------------|

| 3.3 Monitoring infrastructure                                                                              | 52                 |

| 3.3.1 Safety-related Statistics Unit (SafeSU)                                                              | 52                 |

| 3.3.2 Time Contract Monitoring Co-Processor (TCPP)                                                         | 54                 |

| 3.3.3 Context-Aware PMC (CA-PMC)                                                                           | 55                 |

| 3.3.4 Run-time power monitoring instrumentation (RTPM)                                                     | 56                 |

| 3.4 SIMD/Vector, AI accelerator and tensor processor unit de                                               | esign 58           |

| 3.4.1 Tensor Processing Unit                                                                               | 58                 |

| 3.4.2 Parallel Compute Engine                                                                              | 59                 |

| 3.4.3 AI/ML Accelerator                                                                                    | 61                 |

| 3.4.4 Vector Processing Unit (with multi-precision capabilities)                                           | 63                 |

| 3.4.5 CNN Accelerator for an Event-based Sparse Neural Networks                                            | 64                 |

| 3.5 Cryptographic and security accelerators                                                                | 66                 |

| 3.5.1 HLS-based Post-Quantum Cryptographic Accelerator (HLS-PQC)                                           | 66                 |

| 3.5.2 A Multipurpose Accelerator for PQC (PQC-MA)                                                          | 67                 |

| 3.5.3 Accelerator for post-quantum key encapsulation mechanism BIKE                                        | (ACC-BIKE) 69      |

| 3.6 Signal processing, neuromorphic and application-specifi                                                | ic instruction set |

| processors 70                                                                                              | 70                 |

| 3.6.1 Motor Control accelerator                                                                            | 70                 |

| 3.6.2 SCA                                                                                                  | 72                 |

| 3.6.3 LDPC                                                                                                 | 73<br>74           |

| <ul><li>3.6.4 Neuromorphic HW Accelerator</li><li><b>4</b> Operating systems and applications SW</li></ul> | 74                 |

| 4 Operating systems and applications SW<br>4.1 System SW design, implementation and testing                | 76                 |

| 4.1.1 Risc-V-NN                                                                                            | 76                 |

| 4.1.1 Kisc-v-NN<br>4.1.2 AI/ML accelerator driver                                                          | 78                 |

| 4.1.3 Optimization of WebAssembly Interpreter                                                              | 80                 |

| 4.1.4 Driver for Floating-Point Unit and Saftey Island                                                     | 81                 |

| 4.1.5 Use of device tree abstraction for Linux on RISC-V                                                   | 82                 |

| 4.1.6 Execution Framework for Space edge computing                                                         | 83                 |

| 4.1.7 Development and Execution Framework for Automotive                                                   | 84                 |

| 4.1.8 Evaluation of TRISTAN software ecosystem results for ISOLDE us                                       |                    |

| 4.2 Application development tools design, implementation and testin                                        | •                  |

| 4.2.1 Deployment Flow                                                                                      | 86                 |

| 4.2.2 RF-SP: Resource-efficient IoT data processing and analytics                                          | 88                 |

| 4.2.3 Model-based generation framework for hardware safety pattern                                         | 90                 |

| 4.2.4 Automated Precision Tuning Compiler                                                                  | 92                 |

| 4.2.5 AI/ML Accelerator Compiler Toolchain                                                                 | 94                 |

| 4.2.6 TPU HAL                                                                                              | 95                 |

| 4.2.7 HAL for RoT unit as a secure-coprocessor                                                             | 96                 |

| 4.2.8 CFI software algorithm in OT firmware                                                                | 97                 |

| 4.2.9 OT-based secure boot support (TitanBoot)                                                             | 98                 |

| 4.2.10 OpenML Lite Offloading                                                                              | 99                 |

| 4.2.11 LLVM and debugger support for Forward-edge CFI                                                      | 101                |

| D1.2 ISOLDE - confidential                                                                                 | 31.10.2023         |

| 4.2.12 LLVM and debugger support for backward-edge CFI                            | 103 |

|-----------------------------------------------------------------------------------|-----|

| 4.2.13 LLVM and debugger support for cryptographically tagged memory              | 105 |

| 4.2.14 Debugger support for enclave memory isolation                              | 106 |

| 4.2.15 LLVM/MLIR Extensions for PQC Accelerator                                   | 107 |

| 4.3 SW for HW design and validation                                               | 108 |

| 4.3.1 Extra-functional simulation                                                 | 108 |

| 4.3.2 Time Contract Co-processor Compiler                                         | 110 |

| 4.3.3 Power/Performance Modeling for Design Space Exploration PPM-DSE             | 111 |

| 4.3.4 Fault-injection tools for robustness evaluation FFI-RE                      | 113 |

| 4.3.5 SoC simulator for Rocket Chip toolchain                                     | 115 |

| 4.3.6 Software simulator for the AI/ML Accelerator                                | 117 |

| 4.3.7 Fault-injection RTL-simulation                                              | 118 |

| 4.3.8 Open Source Simulation Framework (IFX WI4.3.*)                              | 119 |

| 4.3.9 Tooling to ensure compliance with multicore timing certification objectives | 120 |

| 4.3.10 Tool based on the LLVM compiler to provide WCET estimations                | 123 |

| 4.3.11 Safety analysis of Safety Island by Fault injection                        | 124 |

| 5 Conclusions                                                                     | 125 |

# **Executive Summary**

This Deliverable reports an initial list of requirements and specifications for the various components developed in the context of the ISOLDE project relative to core architecture, hardware and software modules. In addition, this Deliverable provides a first indication about the IP corresponding to each component. A consolidated version of this document will be produced as a follow-up Deliverable D1.4. All partners involved in Tasks 1.2, 1.3 and 1.4 contributed to this Deliverable.

# 1Introduction

Working in the spirit of a hardware / software co-design approach, Deliverable D1.2 "Requirements and specifications on architecture, hardware and software modules and IPs" provides an initial list of requirements on the different components developed in the context of the ISOLDE project, building on the previous D1.1 "Demonstrator requirements and specifications".

The document is organized as follows:

- Section 2 focuses on the architectures, I.e. the components developed in WP2, whose requirements have been collected as part of the work done in Task 1.2;

- Section 3 focuses on hardware / accelerators, I.e. the components developed in WP3, whose requirements have been collected as part of the work done in Task 1.3;

- Section 4 focuses on software, I.e. the components developed in WP4, whose requirements have been collected as part of the work done in Task 1.4.

Each Section is divided according to the Tasks of the associated WP. For each Task, all partners involved contributed by inserting specific sub-subsections for each individual component developed. Each component is uniquely named and is described according to the following structure:

- An initial short description of the component;

- A brief motivation detailing why the component may be needed;

- An indication of the tentative demonstrator (Aerospace, Automotive, Smart Home, IoT) the component should be used for;

- A list of partners involved in the development of the component;

- The license associated to the component;

- List of dependencies to previous / other components;

- List of requirements, identified by a unique id and supplemented by means of verification and type of requirement (**PR:** Performance, **F:** Functional, **PH:** physical, **STD:** compliance to standards);

- Optional additional comments.

This Deliverable is intended to be an initial version of the requirements; a consolidated list of requirements will be provided in a later Deliverable D1.4.

# 1.1 Definitions and Acronyms

| Abbreviation | Description                          |  |

|--------------|--------------------------------------|--|

| AI           | Artificial Intelligence              |  |

| API          | Application Programming Interface    |  |

| AXI          | Advanced eXtensible Interface        |  |

| BCFI         | Backward-edge Control Flow Integrity |  |

| BSP          | Board Support Package                |  |

| CNN          | Convolutional Neural Network         |  |

| CPU          | Central Processing Unit              |  |

| СТМ          | Cryptographically Tagged Memory      |  |

| DSE          | Design Space Exploration             |  |

| EDA          | Electronic Design Automation         |  |

| EMI          | Enclave Memory Isolation             |  |

| FCFI         | Forward-edge Control Flow Integrity  |  |

| FPGA         | Field-Programmable Gate Array        |  |

| FPU          | Floating Point Unit                  |  |

| HAL          | Hardware Abstraction Layer           |  |

| IDE          | Integrated Development Environment   |  |

| IP           | Intellectual Property                |  |

| ISA          | Instruction Set Architecture         |  |

| JIT          | Just-in-Time                         |  |

| ML           | Machine Learning                     |  |

| NN           | Neural Network                       |  |

| NoC          | Network-on-Chip                      |  |

| PMC          | Performance Monitoring Counter       |  |

| PQC          | Post Quantum Cryptography            |  |

| RISC-V       | Specific Open-Sourced RISC ISA       |  |

| RTL          | Register Transfer Level              |  |

| SAL          | Software Abstraction Layer           |  |

| SIMD         | Single Instruction Multiple Data     |  |

| SoC          | System on Chip                       |  |

| TPU          | Tensor Process Unit                  |  |

| VM           | Virtual Machine                      |  |

| VPU          | Vector Process Unit                  |  |

| WCET         | Worst-Case Execution Time            |  |

| XNG          | XtratuM Next Generation              |  |

# 2 Cores, interfaces, peripherals & NoCs

This section will focus on requirements and specifications definition related to the extension of the processor cores, interfaces, peripherals and Network-on-Chip (NoC) IP cores developed in the scope of the ISOLDE project. A set of requirements will be generated for the extension of the processor cores (CVA6 and NOEL-V) and SoC infrastructure (interconnect and peripheral) that are needed for the demonstrator designs or otherwise proposed or planned to be developed within ISOLDE.

#### 2.1 Processors

#### 2.1.1 NOEL-V processor extensions

#### DESCRIPTION

The NOEL-V processor will be extended to support the following features:

- Support for shadow stack (Zicfiss) and Landing pad (Zicfilp) RISC-V extensions.

- Extend NOEL-V processor system to support trusted execution environment.

- Generate IP-XACT description for the NOEL-V subsystem.

#### MOTIVATION

To support the increased demand for security in the space domain Control-flow Integrity (CFI) and trusted execution environment (TEE) are key features. Control-flow Integrity (CFI) capabilities help defend against Return-Oriented Programming (ROP) and Call/Jump-Oriented Programming (COP/JOP) attacks.

| TARGET DEMONSTRATORS |

|----------------------|

| Space, Automotive    |

|                      |

|                      |

| IMPLEMENTERS |

|--------------|

| GSL          |

|              |

| LICENSE |  |

|---------|--|

| GPL     |  |

| LINK TO OTHER MODULES AND IPs |

|-------------------------------|

| TBD                           |

| REQUIREMENTS |      |                                                                             |                                        |

|--------------|------|-----------------------------------------------------------------------------|----------------------------------------|

| ID           | TYPE | DESCRIPTION                                                                 | VERIFICATION                           |

| NV-CFI-01    | STD  | The ratified version of the Zicfiss<br>and Zicfilp shall be<br>implemented. | Simulation (RISC-V architecture test). |

| NV-TEE-01    | F    | Support isolated execution.                                                 | Simulations and FPGA prototyping.      |

| NV-CRY-01 | F   | Support RISC-V Cryptography<br>Extensions.                   | Simulations and FPGA prototyping.                             |

|-----------|-----|--------------------------------------------------------------|---------------------------------------------------------------|

| NV-IPX-01 | STD | The IP description shall be done using the IP-XACT standard. | Integration in EDA tools<br>supporting IP-XACT<br>components. |

#### COMMENTS

The CFI RISC-V standard is not ratified at the time these requirements are specified. The process to define a RISC-V standard for TEE (similar to WorldGuard) is at this time still ongoing.

#### 2.1.2 CVA6 processor extensions

#### DESCRIPTION

The CVA6 processor will be extended to support the following features:

• Support for post quantum cryptography extensions.

#### MOTIVATION

To support the increased demand for security due to quantum computing threat, support of post quantum cryptography is a must for the future.

| TARGET DEMONSTRATORS |

|----------------------|

| Smart home           |

|                      |

IMPLEMENTERS TDIS

# LICENSE Permissive open source (Solderpad)

| LINK TO OTHER MODULES AND IPs |  |

|-------------------------------|--|

| TBD                           |  |

|             |      | REQUIREMENTS                                                                            |              |

|-------------|------|-----------------------------------------------------------------------------------------|--------------|

| ID          | TYPE | DESCRIPTION                                                                             | VERIFICATION |

| CVA6-PQC-01 | STD  | Instructions to support PQC<br>algorithms standardised by NIST<br>shall be implemented. | Simulation   |

| COMMENTS |

|----------|

|----------|

Depending on the instructions that will be defined in future RISC-V PQC extension, support of additional custom instructions can be provided.

#### 2.1.3 CV32E40X processor extensions

#### DESCRIPTION

The goal is to accelerate bytecode virtual machines, in particular WebAssembly. For that, the CV32E40X processor will be extended to support the following features:

- Support for 32-bit Pointer Masking (Xjpm32) RISC-V extensions.

- Memory isolation for bytecode virtual machines

- Computed gotos for bytecode virtual machines

- Hardware-assisted stacks for bytecode virtualization

- Microcode-generator for bytecode VMs

#### MOTIVATION

Bytecode Virtual Machines provide excellent isolation and portability properties. WebAssembly is an interesting bytecode VM for embedded use cases too. JIT techniques are not applicable on resource-constrained devices, and the acceleration of Interpreters is desirable.

#### TARGET DEMONSTRATORS

Smart Home, Automotive

| IMPLEMENTERS |  |

|--------------|--|

|              |  |

| HM           |  |

|              |  |

|              |  |

| LICENSE |  |

|---------|--|

| MIT     |  |

#### LINK TO OTHER MODULES AND IPs

- None

|               |      | REQUIREMENTS                                                                |                                        |

|---------------|------|-----------------------------------------------------------------------------|----------------------------------------|

| ID            | TYPE | DESCRIPTION                                                                 | VERIFICATION                           |

| BYTEC-JPM-01  | STD  | Draft proposal of 32-bit Pointer<br>Masking.                                | Simulation (RISC-V architecture test). |

| BYTEC-GOTO-01 | F    | Method for computed goto<br>support for WebAssembly                         | Simulations and FPGA prototyping.      |

| BYTEC-HWS-01  | F    | Method for hardware-assisted<br>VM stack                                    | Simulations and FPGA prototyping.      |

| BYTEC-BYTE-01 | F    | Method for microcode<br>generation from re-configurable<br>microcode memory | Simulations and FPGA prototyping.      |

| COMMENTS |  |

|----------|--|

|          |  |

#### 2.1.4 Testing Design Parameters for CVA6

#### DESCRIPTION

Creation of CVA6 of different multicore architectures by systems-on-chip generator tools. For this purpose, various design parameters are systematically created according to the specifications of T1.3/T1.4 and compared with each other using various design metrics (computing power, power consumption, etc.) and the suitable design parameters are identified.

|                                                                 |      | MOTIVATION             |                                   |

|-----------------------------------------------------------------|------|------------------------|-----------------------------------|

| Gain Information about proper design parameters for RISC-V SoCs |      |                        | for RISC-V SoCs                   |

|                                                                 |      | TARGET DEMONSTRATORS   |                                   |

|                                                                 |      |                        |                                   |

|                                                                 |      | Smart Home, Automotive |                                   |

| IMPLEMENTERS                                                    |      |                        |                                   |

|                                                                 |      | UZL                    |                                   |

|                                                                 |      |                        |                                   |

| LICENSE                                                         |      |                        |                                   |

| Open Source (TBD)                                               |      |                        |                                   |

| LINK TO OTHER MODULES AND IPs                                   |      |                        |                                   |

| -                                                               |      |                        |                                   |

|                                                                 |      | REQUIREMENTS           |                                   |

| ID                                                              | TYPE | DESCRIPTION            | VERIFICATION                      |

| DSE-SOC-01                                                      | Р    | SoC Design Parameters  | Simulation and FPGA-<br>Prototype |

|                                                                 |      | COMMENTS               |                                   |

|                                                                 |      |                        |                                   |

#### 2.1.5 Analysis Framework (IFX WI2.1.1-2.1.3)

#### DESCRIPTION

Analysis Framework for RISC-V Cores

#### MOTIVATION

Even if there are broad benchmarks as DMIPS widely used, cores normally have their strength and weakness. A more detailed analysis shall give better insights.

Further, processor performance depends on SoC or CPU Subsystem Architectures an Compiler usage, also these influences shall be measured.

| TARGET DEMONSTRATORS |  |

|----------------------|--|

| Automotive           |  |

|                      |  |

| IMPLEMENTERS |

|--------------|

| IFX          |

|              |

| LICENSE     |  |

|-------------|--|

| Proprietary |  |

#### LINK TO OTHER MODULES AND IPs

|          | REQUIREMENTS |                                                           |                                   |  |

|----------|--------------|-----------------------------------------------------------|-----------------------------------|--|

| ID       | TYPE         | DESCRIPTION                                               | VERIFICATION                      |  |

| AHBcb-01 | F/STD        | Have a list of features and<br>variants to be analyzed    | Review                            |  |

| AHBcd-02 | F            | Have a list of testcases that form the analysis framework | Review                            |  |

| AHBcb-03 | F            | Have a concept and use mode<br>for the analysis framework | Work                              |  |

| AHBcd-04 | F            | Have a fully automated analysis                           | Simulation of interrupt scenarios |  |

|                                  | COMMENTS |

|----------------------------------|----------|

| Follow-up RISC-V Standardization |          |

# 2.2 Peripheral and interconnect

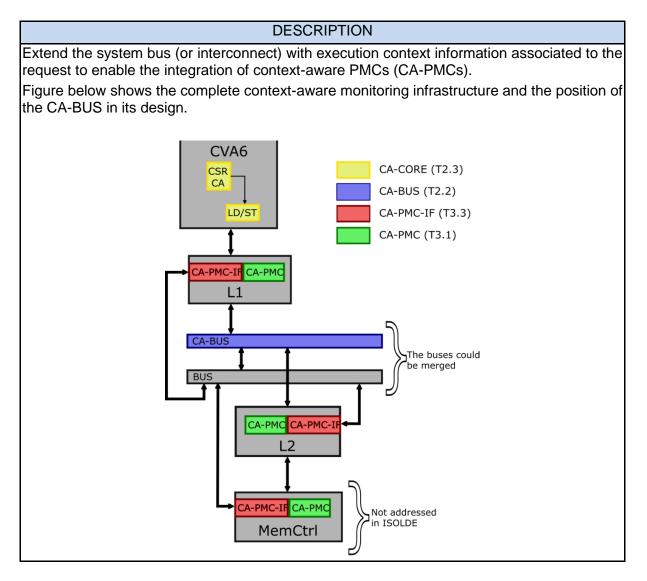

## 2.2.1 Context-Aware Bus (CA-BUS)

# MOTIVATION

Performance Monitoring Counters (PMCs) are essential tools for the verification and monitoring of a system. Safety systems heavily rely on them to implement different safety features. However, they are typically limited, collecting information of every event happening, which puts constraints or limitation on the implementation of the safety mechanisms and/or the system itself. Context-Aware PMCs (CA-PMCs) and the associated infrastructure (CA-CORE, CA-BUS and CA-PMC-IF) will enhance current PMCs and enable more efficient safety verification and monitoring of the system. CA-PMCs will allow the software (typically the OS/Hypervisor) to define the events that need to be collected.

CA-PMCs require the context information to operate, and the context depends on each request/event. The system bus represents a critical IP to transfer such information. The CA-BUS extension will enable the transfer of the context information added to each core request with the CA-CORE (see Section 2.3 – CA-CORE) to the CA-PMCs (see Section 3.3 – CA-PMC).

| TARGET DEMONSTRATORS |  |

|----------------------|--|

| Space                |  |

| IMPLEMENTERS |

|--------------|

| TRT          |

|              |

| LICENSE      |

| TBD          |

| LINK TO OTHER MODULES AND | IPs |

|---------------------------|-----|

|---------------------------|-----|

CVA6 core developed in T2.1 (see Section 2.1) CA-PMCs developed in T3.3 (see Section 3.3)

\_

| REQUIREMENTS |      |                                                                                  |                                                                      |

|--------------|------|----------------------------------------------------------------------------------|----------------------------------------------------------------------|

| ID           | TYPE | DESCRIPTION                                                                      | VERIFICATION                                                         |

| CA-BUS-01    | STD  | The implementation should be<br>compatible with the AXI<br>standard.             | Compatibility with SoC FPGA design using AXI system bus.             |

| CA-BUS-02    | PH   | The size of the context<br>information should be<br>configurable at design time. | Synthesis of designs with<br>different context information<br>sizes. |

| COMMENTS |  |

|----------|--|

|          |  |

#### 2.2.2 Wormhole NoC

#### DESCRIPTION

Develop a Wormhole Network-on-Chip with support for Virtual Networks and Virtual Channels and extensions for monitoring and debugging

#### MOTIVATION

On the one hand, NoCs are scalable interconnect solutions to SoC designs requiring many IP cores. On the other hand, a SoC design could require more than one NoC. In this case, there are basically two options to address that aspect in NoC design: I) the designer can replicate the NoC physically, keeping a simple router. II) the designer can opt to a more complex router with support for VNs and VCs, such that there is a single physical NoC. In general, the combination of VNs/VCs will help to diminish network contention and provide a good degree of Quality of Service, while maintaining area usage for the interconnect controllable.

| TARGET DEMONSTRATORS                |  |

|-------------------------------------|--|

| TBD                                 |  |

|                                     |  |

| IMPLEMENTERS                        |  |

| UPV                                 |  |

|                                     |  |

| LICENSE                             |  |

| MIT (or another permissive license) |  |

#### LINK TO OTHER MODULES AND IPs

Not applicable. The IP does not rely on any other tasks

| REQUIREMENTS |       |                                                             |                                                                                                       |

|--------------|-------|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| ID           | TYPE  | DESCRIPTION                                                 | VERIFICATION                                                                                          |

| WormNoC-01   | F/STD | Support for AXI interfaces                                  | Simulation of external IPs<br>exchanging data through the<br>network using standard AXI<br>interfaces |

| WormNoC-02   | F     | Bandwidth reservation to<br>support different levels of QoS | Simulation testbench using<br>synthetic traffic                                                       |

| WormNoC-03   | F     | Physical traffic isolation                                  | Simulation testbench using<br>synthetic traffic                                                       |

| WormNoC-04   | F     | Support for monitoring traffic-<br>related metrics          | Simulation testbench using<br>synthetic traffic                                                       |

| COMMENTS     |       |                                                             |                                                                                                       |

#### 2.2.3 AXI Sniffer

# DESCRIPTION

Hardware module to monitor AXI traffic

#### MOTIVATION

Safety-related applications require deriving execution time bound for the different software components. This is challenged by the existence of timing interferences in heterogeneous multicore SoCs. Timing monitoring and enforcement is a well-known approach to control execution time interference. The AXI sniffer will enable extracting request-level interference in interconnects usings AXI interfaces.

| TARGET DEMONSTRATORS                |

|-------------------------------------|

| TBD                                 |

|                                     |

| IMPLEMENTERS                        |

| UPV                                 |

|                                     |

| LICENSE                             |

| MIT (or another permissive license) |

|                                     |

| LINK TO OTHER MODULES AND IPs       |

Not applicable. The IP does not rely on any other tasks

| REQUIREMENTS  |       |                                                     |                                                                              |

|---------------|-------|-----------------------------------------------------|------------------------------------------------------------------------------|

| ID            | TYPE  | DESCRIPTION                                         | VERIFICATION                                                                 |

| AXISniffer-01 | F/STD | Seamless Integration in AXI-<br>based Interconnects | Integration and validation of<br>the module in complete SoC<br>demonstrators |

| AXISniffer-02 | F     | Communication with global monitoring units          | Integration and validation of<br>the module in complete SoC<br>demonstrators |

| COMMENTS      |       |                                                     |                                                                              |

#### 2.2.4 AHB Crossbar (IFX WI2.2.1-2.2.3)

#### DESCRIPTION

Develop an AHB crossbar generally usable for different number of initiators and responders. *Please note "master" and "slave" has been widely used, fortunately more and more these terms are replaced. I used here "initiator" and "responder". As these terms are not fully aligned, we should agree in Isolde on consistent names.*

#### MOTIVATION

AHB is the standard bus used

| TARGET DEMONSTRATORS |

|----------------------|

| Automotive           |

|                      |

IMPLEMENTERS

| IFX     |  |

|---------|--|

|         |  |

| LICENSE |  |

TBD

#### LINK TO OTHER MODULES AND IPs

IPs that want to connect to the crossbar must follow AHB specification, some adjustment/classification of AHB interfaces may be needed.

| REQUIREMENTS |       |                                                  |                                                           |

|--------------|-------|--------------------------------------------------|-----------------------------------------------------------|

| ID           | TYPE  | DESCRIPTION                                      | VERIFICATION                                              |

| AHBcb-01     | F/STD | Support for AHB interfaces                       | Simulation of crossbar stand alone and with connected IPs |

| AHBcd-02     | F     | Different number of Initiators<br>and Responders | Simulation testbench using<br>synthetic traffic           |

| AHBcb-03     | F     | Prioritization                                   | Simulation testbench using<br>synthetic traffic           |

| AHBcd-04     | F     | Support for privileged support                   | Simulation testbench using synthetic traffic              |

## COMMENTS

# 2.2.5 AHB/APB Interrupt Controller (IFX WI2.2.4-2.2.5)

| DESCRIPTION                                        |

|----------------------------------------------------|

| Develop an AHB Interrupt Controller for RISC-V SoC |

#### MOTIVATION

AHB is the standard bus used, interrupt is a standard feature being provided with RISC-V

| TARGET DEMONSTRATORS |  |

|----------------------|--|

| Automotive           |  |

| IMPLEMENTERS |  |

|--------------|--|

| IFX          |  |

| LICENSE |

|---------|

| TBD     |

#### LINK TO OTHER MODULES AND IPs

Follow the CLINT discussions and decide if an RISC-V internal interrupt is the better way to go.

| REQUIREMENTS |       |                                                         |                                   |

|--------------|-------|---------------------------------------------------------|-----------------------------------|

| ID           | TYPE  | DESCRIPTION                                             | VERIFICATION                      |

| AHBcb-01     | F/STD | Decide on external interrupts                           | Simulation of use cases           |

| AHBcd-02     | F     | Different number of interrupts<br>and priorities        | Simulation of interrupt scenarios |

| AHBcb-03     | F     | Different ways of Interrupt<br>Service Address handling | Simulation of interrupt scenarios |

| AHBcd-04     | F     | Make Interrupt controller robust                        | Simulation of interrupt scenarios |

|                                  | COMMENTS |

|----------------------------------|----------|

| Follow-up RISC-V Standardization |          |

# 2.2.6 AHB/APB Timer (IFX WI2.2.6-2.2.7)

| DESCRIPTION                         |

|-------------------------------------|

| Develop an AHB-Timer for RISC-V SoC |

MOTIVATION

AHB is the standard bus used, timer is a standard feature being provided with RISC-V

| TARGET DEMONSTRATORS |

|----------------------|

| Automotive           |

IMPLEMENTERS IFX

| LICENSE |  |

|---------|--|

| TBD     |  |

#### LINK TO OTHER MODULES AND IPs

Analyse the internal timer features and decide on internal/external solution.

|          |       | REQUIREMENTS                                  |                                   |

|----------|-------|-----------------------------------------------|-----------------------------------|

| ID       | TYPE  | DESCRIPTION                                   | VERIFICATION                      |

| AHBcb-01 | F/STD | Decide on external timer                      | Simulation of use cases           |

| AHBcd-02 | F     | Different number of timer<br>channels         | Simulation of interrupt scenarios |

| AHBcb-03 | F     | Different use cases: Watchdog,<br>Clock, PWM, | Simulation of interrupt scenarios |

| AHBcd-04 | F     | Make Timer robust                             | Simulation of interrupt scenarios |

|                                  | COMMENTS |

|----------------------------------|----------|

| Follow-up RISC-V Standardization |          |

## 2.2.7 GRLIB IP library

DESCRIPTION Provide access to the GRLIB IP library to be used as SoC building blocks for the demonstrators. Extend TBD IP to meet demonstrator needs.

# MOTIVATION

GRLIB provides a variety of IP cores under GLP license.

| TARGET DEMONSTRATORS |

|----------------------|

| All                  |

| IMPLEMENTERS |  |

|--------------|--|

| GSL          |  |

| LICENSE |  |

|---------|--|

| GPL     |  |

|      | LINK TO OTHER MODULES AND IPs |

|------|-------------------------------|

| None |                               |

|             |      | REQUIREMENTS   |              |

|-------------|------|----------------|--------------|

| ID          | TYPE | DESCRIPTION    | VERIFICATION |

| GRLIB-IP-01 | F    | Extend TBD IP. |              |

#### COMMENTS

Work can be done to extend GRLIB IP requested by demonstrators.

#### 2.3 Common extension interfaces

#### 2.3.1 Context-Aware CORE Extensions (CA-CORE)

#### DESCRIPTION

Extend core design with register (CSR) to define current context information and transfer this information to each request issued by the core. Refer to Figure [Section 2.2 – CA-BUS] for a description of the context-aware monitoring and the position of the CA-CORE in its design.

#### MOTIVATION

Performance Monitoring Counters (PMCs) are essential tools for the verification and monitoring of a system. Safety systems heavily rely on them to implement different safety features. However, they are typically limited, collecting information of every event happening, which puts constraints or limitations on the implementation of the safety mechanisms and/or the system itself. Context-Aware PMCs (CA-PMCs) and the associated infrastructure (CA-CORE, CA-BUS and CA-PMC-IF) will enhance current PMCs and enable more efficient safety verification and monitoring of the system. CA-PMCs will allow the software (typically the OS/Hypervisor) to define the events that need to be collected.

In order to implement context-aware PMCs (CA-PMCs, see Section 3.3) the cores require providing the context information with each request: The CA-CORE extension will integrate the current context information (e.g. stored in a dedicated CSR) to each of the request issued by the core, effectively extending the request interface.

|       | TARGET DEMONSTRATORS |  |

|-------|----------------------|--|

| Space | Space                |  |

| IMPLEMENTERS |

|--------------|

| TRT          |

| LICENSE |

|---------|

| TBD     |

#### LINK TO OTHER MODULES AND IPs

- CVA6 core developed in T2.1 (see Section 2.1)

- BUS-CA developed in T2.2 (see Section 2.2)

- CA-PMCs developed in T3.3 (see Section 3.3)

- CA-PMCs interface developed in T3.1 (see Section 3.1)

|            |      | REQUIREMENTS                                                                        |                                |

|------------|------|-------------------------------------------------------------------------------------|--------------------------------|

| ID         | TYPE | DESCRIPTION                                                                         | VERIFICATION                   |

| CA-CORE-01 | STD  | The context-aware information<br>should be implemented using<br>the CSRs interface. | Unit tests in SoC FPGA design. |

| CA-CORE-02 | F             | The size of the context<br>information should be<br>configurable at design time.                                                                                                             | Synthesis of designs with<br>different context information<br>sizes. |

|------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| CA-CORE-03 | CA-CORE-03 PR | The integration of the context<br>information into the ld/st request<br>should not have performance<br>penalties (i.e. same number of<br>cycles with or without the<br>context information). | Simulation measurements.                                             |

# COMMENTS

#### 2.3.2 Memory bank interface

DESCRIPTION

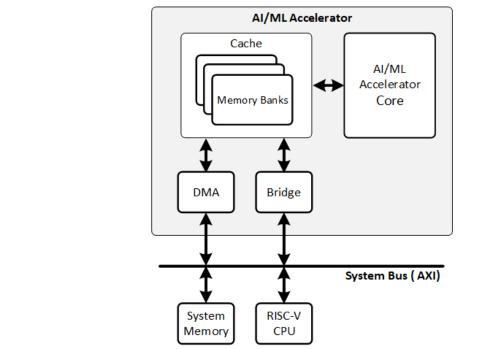

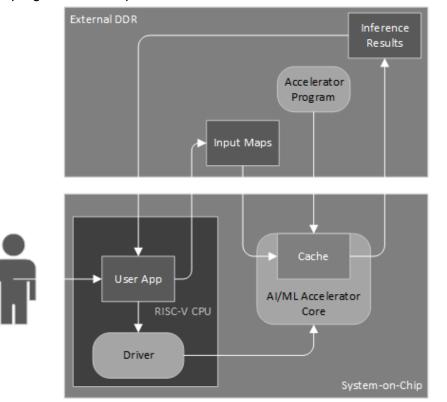

The cache of the AI/ML accelerator is organized into several memory banks. The memory bank's content can be accessed using a simple memory bank interface. Transactions consist of two phases: address phase and data phase, making this interface easy to adapt to another standard interface.

Connecting a RISC-V core directly to the banks using this interface enables tighter integration and more efficient data transfers between the core and the accelerator.

## MOTIVATION

Allowing the RISC-V core to directly access the Al/ML accelerator memory banks means that the accelerator does not need to save or load intermediary results to/from a system memory (e.g., DDR or L2 cache). This has the following advantages:

- Quick access to data stored in the banks. No need to transfer intermediate data to system memory.

- High bandwidth. Up to 256 bit per clock cycle to feed a SIMD module of the core.

- Random access to any location in the banks. The memory banks address space is mapped into the RISC-V address space.

- Much lower power as no transactions to intermediate memories are needed.

- Tighter integration of the RISC-V core with the AI/ML accelerator. The RISC-V core can perform data processing that is not supported by the accelerator.

# TARGET DEMONSTRATORS

Automotive

#### IMPLEMENTERS

XPERI

LICENSE

# Open Source (license TBD)

# LINK TO OTHER MODULES AND IPs

CVA6 or NOEL-V cores (T2.1) and AI/ML accelerator (T3.4)

| REQUIREMENTS |      |                                           | 3                     |

|--------------|------|-------------------------------------------|-----------------------|

| ID           | TYPE | DESCRIPTION                               | VERIFICATION          |

| MB-IF-01     | F    | RISC-V core R/W access to<br>memory bank  | HW verification tests |

| MB-IF-02     | STD  | AXI Protocol Standard                     | HW verification tests |

| MB-IF-03     | PR   | Memory bank read transfer<br>performance  | HW verification tests |

| MB-IF-04     | PR   | Memory bank write transfer<br>performance | HW verification tests |

COMMENTS

-

#### 2.3.3 Extension interface for NOEL-V

#### DESCRIPTION

Extend the NOEL-V processor with an extension/co-processor interface to support integration of third-party accelerators.

# MOTIVATION

A standardized extension interface is essential for easy integration of tightly coupled accelerator IPs to the processor core. With this interface, the processor core can be extended with additional features (e.g. Vector processing unit VPU, other custom extensions) without modifying the actual processor core.

| TARGET DEMONSTRATORS |

|----------------------|

| Space, Automotive    |

|                      |

| IMPLEMENTERS |

|--------------|

| GSL          |

|              |

| LICENSE |  |

|---------|--|

| GPL     |  |

| LINK TO OTHER MODULES AND IPs                               |  |

|-------------------------------------------------------------|--|

| <ul> <li>VPU developed in T3.4 (see Section TBD)</li> </ul> |  |

|           |      | REQUIREMENTS                                                 |                                  |

|-----------|------|--------------------------------------------------------------|----------------------------------|

| ID        | TYPE | DESCRIPTION                                                  | VERIFICATION                     |

| NV-XIF-01 | STD  | The extension interface should<br>implement an open standard |                                  |

| NV-XIF-02 | F    | The interface should support<br>integration with a VPU       | Simulation and FPGA prototyping. |

| COMMENTS                                                               |

|------------------------------------------------------------------------|

| The specification for the extension interface to be used is still TBD. |

#### 2.3.4 Extension interface for CVA6

#### DESCRIPTION

Revisit the currently implemented CV-X-IF extension interface on CVA6 to support integration of third-party accelerators.

# MOTIVATION

A standardized extension interface is essential for easy integration of tightly coupled accelerator IPs to the processor core. With this interface, the processor core can be extended with additional features like post-quantum cryptography co-processor or vector co-processor without modifying the existing processor core.

| TARGET DEMONSTRATORS |

|----------------------|

| Smart home           |

|                      |

IMPLEMENTERS TDIS

| LICENSE                            |

|------------------------------------|

| Permissive open source (Solderpad) |

| LINK TO OTHER MODULES AND IPs                    |  |

|--------------------------------------------------|--|

| Accelerators (3.4.1, 3.4.2, 3.4.3, 3.4.4, 3.6.4) |  |

|             |      | REQUIREMENTS                                                              |                                  |

|-------------|------|---------------------------------------------------------------------------|----------------------------------|

| ID          | TYPE | DESCRIPTION                                                               | VERIFICATION                     |

| CVA6-XIF-01 | STD  | The extension interface should<br>implement an open standard              |                                  |

| CVA6-XIF-02 | F    | The interface should support<br>integration with vector co-<br>processor. | Simulation and FPGA prototyping. |

| COMMENTS                                                               |

|------------------------------------------------------------------------|

| The specification for the extension interface to be used is still TBD. |

#### 2.3.5 Extension interface between CVA6 and Vector accelerator

DESCRIPTION Tune the CV-X-IF extension interface on CVA6 to support integration of third-party accelerators (e.g., vector accelerator).

#### MOTIVATION

A standardized extension interface like the CV-X-IF is essential for easy integration of tightly coupled accelerator IPs to the processor core. The current CV-X-IF specifications likely need to be tuned to take into account the needs of complex accelerators with specific requirements on their load-store unit and/or register file.

| TARGET DEMONSTRATORS |  |

|----------------------|--|

| IoT                  |  |

|                      |  |

| IMPLEMENTERS |

|--------------|

| ETHZ         |

|              |

| LICENSE                            |

|------------------------------------|

| Permissive open source (Solderpad) |

| LINK TO OTHER MODULES AND IPs |

|-------------------------------|

| 2.3.4                         |

| REQUIREMENTS  |      |                                                                           |                           |

|---------------|------|---------------------------------------------------------------------------|---------------------------|

| ID            | TYPE | DESCRIPTION                                                               | VERIFICATION              |

| CVA6-V-XIF-01 | F    | The interface should support<br>integration with vector co-<br>processor. | Cycle-accurate simulation |

| COMMENTS |  |

|----------|--|

|          |  |

## 2.4 SW interfaces to general purpose cores

#### 2.4.1 XNG NOEL-V BSP update to new standards

#### DESCRIPTION

Development and testing of XNG (XtratuM Next Generation) NOEL-V architectural port to support new standards of RISC-V and new IPs developed in the scope of the project.

#### MOTIVATION

New standards of RISC-V architecture implemented by the NOEL-V core make it interesting to update the XNG RISC-V BSP (Board Support Package) to support all the newest features. Also, it is interesting to integrate inside the hypervisor improvements and new IPs developed inside the scope of this project.

| TARGET DEMONSTRATORS |

|----------------------|

| Space                |

| IMPLEMENTERS         |

| FEN                  |

| LICENSE              |

| Proprietary          |

#### NOEL-V core (T2.1) Other links TBD

| REQUIREMENTS |      |                                                                                                                                                                                                                                            |                                                                    |

|--------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| ID           | TYPE | DESCRIPTION                                                                                                                                                                                                                                | VERIFICATION                                                       |

| XNG-01       | F    | XNG should support Kintex<br>UltraScale FPGA integrating a<br>multicore NOEL-V processor as<br>hardware platform                                                                                                                           | XNG runs on the target<br>platform and functional tests<br>succeed |

| XNG-02       | F    | XNG should integrate the<br>custom interrupt controller<br>developed in the project                                                                                                                                                        | Functional testing                                                 |

| XNG-03       | F    | XNG should support the IOMMU developed in the scope of the project                                                                                                                                                                         | Functional testing by executing specific tests                     |

| XNG-04       | F    | <ul> <li>XNG should provide services (or direct access) to allow the integration of XNG in the RAPITA benchmarks of stress generation on shared resources.</li> <li>Note: this feature could depend on the underlaying hardware</li> </ul> | Functional testing                                                 |

| XNG-05       | F    | XNG should integrate fault<br>injection tests                                                                                                                                                                                              | Functional testing                                                 |

| XNG-06 | F | Fault injection tests periodicity<br>should be configurable in the<br>XNG configuration files (XCF)                        | Functional testing |

|--------|---|----------------------------------------------------------------------------------------------------------------------------|--------------------|

| XNG-07 | F | XNG should implement a health<br>monitor to perform an action<br>previously defined in the XCF<br>when a fault is detected | Functional testing |

#### COMMENTS

- Interrupt controller integration will be addressed in Task 3.1

- IOMMU integration will be addressed in Task 2.2.

- The integration of the RAPITA benchmarks will be addressed in Task 4.3.

- Fault injection tests integration will be addressed in Task 4.3.

#### 2.4.2 CVA-6 multicore experiments and analysis

| DESCRIPTION                                                        |  |

|--------------------------------------------------------------------|--|

| Investigate CVA-6 multicore setups and safety/security properties. |  |

MOTIVATION

Multicore mixed critical systems have a need for resource partitioning (e.g. cache partitioning). We investigate what is available and whether it can/could be used meaningfully in a CVA-6 multicore setup.

| TARGET DEMONSTRATORS |                               |                                                                                                                         |                            |  |

|----------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------|----------------------------|--|

|                      | Space, Automotive, Smart Home |                                                                                                                         |                            |  |

|                      |                               | IMPLEMENTERS                                                                                                            |                            |  |

|                      |                               | SYSGO                                                                                                                   |                            |  |

|                      |                               | LICENSE                                                                                                                 |                            |  |

|                      |                               | TBD                                                                                                                     |                            |  |

|                      | L                             | INK TO OTHER MODULES AND                                                                                                | IPs                        |  |

|                      | Link to CVA-6 activities TBD  |                                                                                                                         |                            |  |

|                      |                               | REQUIREMENTS                                                                                                            |                            |  |

| ID                   | TYPE                          | DESCRIPTION                                                                                                             | VERIFICATION               |  |

| CVAM-01              | F                             | It shall be analyzed whether/how<br>to use multicore for mixed critical<br>systems, also in context of<br>demonstrator. | Report in demonstrator WP. |  |

| COMMENTS             |                               |                                                                                                                         |                            |  |

| None                 |                               |                                                                                                                         |                            |  |

#### 2.4.3 SW Abstraction Layer for RISC-V Processors (IFX WI 2.4.1 2.4.3)

DESCRIPTION Define a software abstraction layer (SAL) that strives for treating different RISC-V cores the same

#### MOTIVATION

New RISC-V variants offer specific solutions in domain specific areas but are that different that parts of the SW stack must be re-written. A common abstraction layer may at least reduce the effort.

| TARGET DEMONSTRATORS |  |

|----------------------|--|

| Automotive           |  |

| IMPLEMENTERS |

|--------------|

| IFX          |

|              |

| LICENSE     |  |

|-------------|--|

| Proprietary |  |

| LINK TO OTHER MODULES AND IPs           |  |

|-----------------------------------------|--|

| NOEL-V core, CVA6 Core, and other cores |  |

|        |      | REQUIREMENTS                                                                                              |                    |

|--------|------|-----------------------------------------------------------------------------------------------------------|--------------------|

| ID     | TYPE | DESCRIPTION                                                                                               | VERIFICATION       |

| SAL-01 | F    | List of differences between<br>processors, either ISA support,<br>ISA extension, CSRs or<br>architectural | Review             |

| SAL-02 | F    | Provide proposal for an abstraction layer for discussion                                                  | Review             |

| SAL-03 | F    | Provide concept for abstraction layer                                                                     | Reviews            |

| SAL-04 | F    | Provide implementation of<br>abstraction layer.                                                           | Functional testing |

| SAL-05 | F    | Measure impact of abstraction layer                                                                       | Functional testing |

| COMMENTS                                                                 |

|--------------------------------------------------------------------------|

| <ul> <li>Processor details may be subject of confidentiality.</li> </ul> |

#### 2.4.4 NOEL-V software tools

DESCRIPTION

Provide bare-metal and Linux RISC-V tool chains for NOEL-V. Extend support for NOEL-V in TBD software.

MOTIVATION

To support building software for NOEL-V targets

| TARGET DEMONSTRATORS |

|----------------------|

| All                  |

|                      |

| IMPLEMENTERS |

|--------------|

| GSL          |

| LICENSE |  |

|---------|--|

| GPL     |  |

| LINK TO OTHER MODULES AND IPs |  |

|-------------------------------|--|

| None                          |  |

|          |      | REQUIREMENTS                               |              |

|----------|------|--------------------------------------------|--------------|

| ID       | TYPE | DESCRIPTION                                | VERIFICATION |

| NV-SW-01 | F    | Extend support for NOEL-V in TBD software. |              |

| COMMENTS                                                                |

|-------------------------------------------------------------------------|

| Work can be done to extend software support requested by demonstrators. |

# **3 Accelerators and extensions**

This section will be devoted to defining functional / non-functional requirements and specifications for the different components related to accelerators and extensions developed in the context of ISOLDE's WP3. These components are divided according to the tasks inside WP3 and include modules for safety and security, accelerator interfaces and infrastructure, modules for infrastructure monitoring, VEC and AI accelerators, cryptographic accelerators and ASIPs and neuromorphic accelerators.

### 3.1 Safety and Security modules

#### 3.1.1 Safety-related Traffic Injector (SafeTI)

#### DESCRIPTION

Integration, enhancement, and documentation of a safety-related traffic injector

#### MOTIVATION

Validating complex SoCs with software-only means or externally (e.g., through JTAG or similar interfaces) poses many challenges to produce relevant traffic scenarios in the internal interconnects. This is mainly due to the inability to generate those traffic patterns by software means, or the fact that they can only be generated with asynchronous events (w.r.t. the computing cores activities), such as Ethernet traffic. This challenges the ability to assess scenarios where specific traffic events occur simultaneously. Having a programmable traffic injector on-chip allows tackling this limitation and achieving appropriate validation for safety-relevant SoCs.

| TARGET DEMONSTRATORS |

|----------------------|

| Automotive           |

| IMPLEMENTERS         |

| BSC                  |

#### LICENSE

MIT (other open-source permissive licenses also possible)

#### LINK TO OTHER MODULES AND IPs

Not applicable. The work does not rely on previous tasks

| REQUIREMENTS        |   |                      |                                                                                                                                   |

|---------------------|---|----------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| ID TYPE DESCRIPTION |   | VERIFICATION         |                                                                                                                                   |

| SafeTI-01           | F | Support for AMBA AXI | Traffic patterns can be<br>programmed, and injected<br>traffic observed in the AXI<br>interface (e.g., by means of<br>simulation) |

| SafeTI-02 | F  | Flexible traffic patterns<br>supported (read/write, variable<br>burst length, variable inter-<br>request delay) | Traffic injected in isolation<br>matches the patterns<br>programmed (e.g., observed<br>in the AXI interface by means<br>of simulation)                                                                                                                                                       |  |

|-----------|----|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SafeTI-03 | PR | Traffic injected by a given core<br>decreases linearly with the size<br>of the SafeTI injected bursts           | A core sending sustained<br>requests through the AXI<br>interface with N cycles<br>between consecutive<br>requests observes an inter-<br>request delay of (B-N) cycles,<br>where B is the minimum<br>number of cycles needed to<br>send a data burst of the size<br>programmed in the SafeTI |  |

|           |    | COMMENTS                                                                                                        |                                                                                                                                                                                                                                                                                              |  |