ISOLDE Project will have high performance RISC-V processing systems and platforms at least at TRL 7 for the vast majority of building blocks, demonstrated for key European application domains such as automotive, space and IoT with the expectation that two years after completion ISOLDE’s high performance components will be used in industrial quality products.

Infineon Technologies AG - Holger Schmidt

Project Duration: 01.05.2023 - 30.04.2026

Email: info![]() isolde-project [dot] eu

isolde-project [dot] eu

Website: https://www.isolde-project.eu

LinkedIn: https://www.linkedin.com/company/isolde-project/

Virtual Repository: https://www.isolde-project.eu/virtual-repository

The ISOLDE consortium recently returned to Munich on February 3-4, 2026, for a project meeting. Bringing together partners from across Europe both in person and online, this gathering once again proved the collective expertise and dedication driving ISOLDE’s mission to develop high-performance RISC-V processing systems for key sectors such as automotive, space, and IoT.

As ISOLDE officially enters its home stretch, this two-day session was focused on strategic alignment. Consortium members shared comprehensive updates on their progress and defined the concluding steps necessary to cement the project's objectives.

A core objective of this meeting was syncing our final project activities. With the finish line in sight, partners participated in targeted workshops to ensure that all independent work packages integrate seamlessly into the final deliverables. These collaborative sessions allowed the team to tackle remaining technical challenges and guarantee that the project's approach culminates in a robust outcome.

The success of this meeting would not have been possible without the active participation and engagement of all consortium members. A big thank you to everyone who contributed their time, and work, whether attending in Munich or connecting virtually.

As we push forward toward our ultimate goal of delivering customizable, high-performance IPs hosted on European servers, we are more aligned than ever to successfully conclude this journey together.

Stay tuned for our final results and upcoming updates as ISOLDE crosses the finish line!

This year, the Austrian RISC-V community launched a collaborative initiative aimed at increasing the visibility and impact of the RISC-V ecosystem. The RISC-V meetup, chaired by Daniel Müller-Gritschneder (TU Wien) and Willibald Krenn (Silicon Austria Labs) has gained strong backing from industry leaders such as NXP Semiconductors and Infineon. Their shared goal: to create a strong platform for exchanging knowledge and fostering deep technical dialogue across academia and industry.

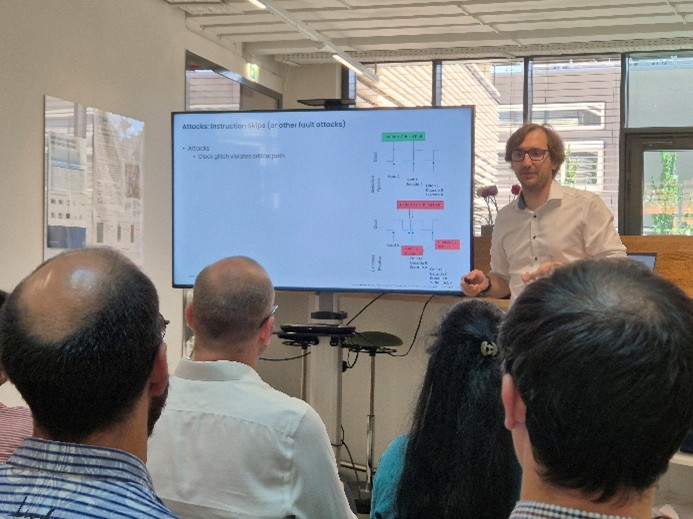

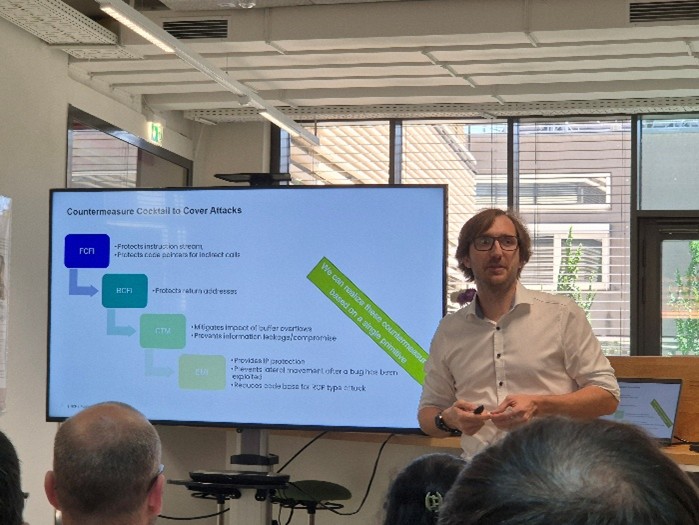

At the second Austrian RISC-V Meetup at Silicon Austria Labs (SAL), Marcel Medwed from NXP in Austria presented the latest developments in microcontroller (MCU) security. His talk focused on how RISC-V instruction set extensions are shaping the future of both physical and logical protection for embedded systems. These efforts are part of the ISOLDE project under the Chips Joint Undertaking, which aims to expand and industrialize the European RISC-V ecosystem.

At the second Austrian RISC-V Meetup at Silicon Austria Labs (SAL), Marcel Medwed from NXP in Austria presented the latest developments in microcontroller (MCU) security. His talk focused on how RISC-V instruction set extensions are shaping the future of both physical and logical protection for embedded systems. These efforts are part of the ISOLDE project under the Chips Joint Undertaking, which aims to expand and industrialize the European RISC-V ecosystem.

The goal? To compete with proprietary alternatives by delivering high-performance, secure processing platforms tailored for automotive, smart cities, mobility, and logistics.

Embedded systems face a range of attacks, from clock and power glitches that can cause timing violations, to memory vulnerabilities like buffer overflows. These attacks can lead to skipped instructions, faulty data, privilege escalation, and even arbitrary code execution.

The challenge lies in designing security mechanisms that are both robust and efficient, minimizing impact on code size and hardware footprint.

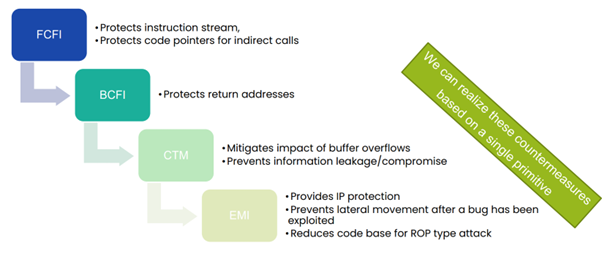

To address these threats, the ISOLDE project has developed a comprehensive suite of RISC-V extensions and custom security mechanisms:

Security for embedded systems must be both effective and lightweight, ensuring robust protection without unnecessarily increasing code size. By leveraging RISC-V instruction set extensions and custom mechanisms, developers can implement targeted and efficient security features. Within the ISOLDE project, a comprehensive "cocktail" of countermeasures has been developed to address both fault-based and software-based attacks, providing a holistic approach to embedded system security.

November 2025 – Advancing its mission to transform Europe's technological landscape, the ISOLDE project is delivering major advancements in high-performance embedded computing, safety, and security through open-source RISC-V processor technology. Bringing together a consortium of 37 partners and 2 associated partners from leading European research institutions and industries, ISOLDE is laying the groundwork for digital sovereignty and semiconductor independence. Funded under the Chips Joint Undertaking (Chips JU) within Horizon Europe, the project is accelerating digital transformation while supporting Europe’s transition toward a green, climate-neutral, and digitally autonomous future.

The ISOLDE project (High Performance, Safe, Secure, Open-Source Leveraged RISC-V Domain-Specific Ecosystems) is advancing European-designed high-performance RISC-V-based CPUs and IP blocks, including accelerators, to Technology Readiness Level (TRL) 8 by project completion. These open-source processor architectures and accelerators will be showcased by demonstrators for key European industries such as automotive, space, and IoT. About two years after completion, first ISOLDE high-performance components are expected to be integrated into industrial-grade products.

To ensure sustainability and accessibility, ISOLDE is initiating an industrial-grade open-source support ecosystem for development, verification, and maintenance. In addition, customizable IPs will be distributed through secure, industrial-grade repositories, ensuring long-term availability and reinforcing the European Union’s commitment to digital sovereignty.

Over the past two years, ISOLDE has reached important milestones in advancing RISC-V-based high-performance computing, safety, and security. These achievements pave the way for Europe’s leadership in open-source semiconductor technology and digital sovereignty. Highlights include:

By strengthening the European RISC-V ecosystem, ISOLDE is making a decisive contribution to unifying and advancing an industry-backed, homegrown open-source architecture for high-performance embedded computing.

As ISOLDE enters its final phase, efforts will focus on tapeout-ready designs, FPGA-based prototypes, expanded industrial collaborations, and preparing the deployment of its solutions. The project’s progress shows that Europe is not only capable of competing in the global semiconductor industry but is also taking a leadership role in open computing innovation.

For more information about ISOLDE and its achievements, visit www.isolde-project.eu.

ISOLDE's Presentation slot is scheduled for:

Thursday, 4 December 2025

13:30 – 13:45, during Networking Lunch

at Booth number 7.

About: EFECS 2025 is the premier European Forum for Electronic Components and Systems, dedicated to advancing the sector’s growth and innovation. Taking place in Malta on December 3-4, 2025, this event brings together industry leaders, policymakers, researchers, and innovators to strengthen Europe’s strategic leadership in semiconductor technology.

The ISOLDE project, funded by the Key Digital Technologies Joint Undertaking (KDT JU), aims to develop European high-performance RISC-V-based CPUs, achieving functional and non-functional improvements to compete with proprietary alternatives or surpass them. Project partners from leading EU universities and companies will develop advanced architectures, novel accelerators, and reusable IPs, forming a robust compute infrastructure for applications in automotive, industrial, and aerospace domains. The ISOLDE project seeks to establish an European sovereignty in semiconductors, closing the confidence gap, and driving adoption through prototype solutions, documentation, and benchmarks.

Within this project, a demonstrator is developed targeting the space use-case, to showcase the IPs developed in ISOLDE and aiming at revolutionizing onboard computational capabilities for space applications by leveraging RISCV cores and accelerators, integrated with an advanced software layer, to create a hardware and software platform capable of meeting the dual challenges of demanding computing and memory requirements and the harsh environmental constraints of space.

A key innovation of the project is to harness the CVA6 processor family and tensor accelerators, all connected through the open standard BUS protocol AXI4, to enable processing capabilities closer to the sensor and support the development of onboard inference capabilities. Compute intensive applications are offloaded to dedicated accelerators controlled by the Cheshire system host and can communicate directly with the memory through dedicated DMAs, relieving the host from unnecessary CPU cycles. This approach aims to transform traditional workflows, where satellite data, such as Earth observation images, undergo initial preprocessing onboard before being transmitted to ground stations for high performance computing. By bringing these processing steps onboard, the project not only minimizes uplink and downlink requirements, but also accelerates real-time decision-making and enhances satellite autonomy.

The space demonstrator targets a low-Earth orbit satellite use-case, inspired by the Sentinel-2 mission, and encompasses a broad range of applications, such as Earth observation, avionic functionalities and attitude orbit control (AOC), and telemetry processing for fault detection, identification, and recovery (FDIR). Beyond these traditional domains, the ISOLDE space demonstrator focuses on artificial intelligence (AI) models to further enhance spacecraft autonomy. These models will be crucial for applications such as wildfire detection from hyperspectral images captured by the multi-spectral instrument (MSI) and FDIR using telemetry data from the Attitude Control System (ACS). The performance of these AI algorithms will be evaluated on the new hardware, showcasing their potential to redefine the role of onboard computing in space systems.

About Leonardo

Leonardo is a global industrial group that creates multi-domain technological capabilities in the Aerospace, Defence and Security sector. With over 60,000 employees worldwide, the company has a significant industrial presence in Italy, the UK, Poland and the US. It also operates in 150 countries through subsidiaries, joint ventures and investments. A key player in major international strategic programmes, it is a technological and industrial partner of governments, defence administrations, institutions and companies. In 2024, Leonardo recorded consolidated revenues of €17.8bn, new orders for €20.9bn and invested €2.5bn in R&D. Innovation, continuous research, digital industry and sustainability are the pillars of its business worldwide.

In the context of the ISOLDE project, Politecnico di Milano (PoliMi) develops approximate computing technologies at the hardware and software level, cryptographic accelerators, and efficiency enhancements for real-time computing. The proposed advances are applied to the Space demonstrator RISC-V-based platform.

Approximate Computing is an emerging paradigm that attempts to improve the energy efficiency of computation, a critical issue for battery-powered embedded systems as well as to address the increasing energy footprint of ICT worldwide, by trading off some of the computation accuracy.

Briefly, in any computer system, all computations are performed with a certain degree of accuracy, i.e., on a fixed number of digits (more precisely, of bits). This number of digits is usually vastly oversized with respect to the actual ranges of the numeric values computed, to minimize the risk of errors.

The TAFFO framework enables the reduction of the data size, as well as the switching between different types of data representations (e.g., floating point, fixed point, etc.) to trade off accuracy that is not actually needed by the computation for lower energy consumption, obtained by employing custom hardware, such as the customized floating point unit also developed by PoliMi, or by adapting to the available hardware characteristics (e.g., switching to fixed point when a hardware floating point unit is not available at all).

With the seTHet and luTHet extensions developed in ISOLDE, TAFFO is also able to efficiently exploit the memory subsystem of an heterogeneous system, by tuning the precision in accordance to the available direct memory access bandwidth and by tabulating costly trigonometric functions instead of computing them.

Considering a Sobel edge detection, a different tuning of the available memory for trigonometric function tabulation minimally affects the quality of the output yielding a 30× speedup and, consequently, a reduction of the total energy by the same factor. The framework then selects the best solution according to the required quality and the available memory.

Politecnico di Milano is the foremost technical university in Italy, with over 45,000 students in engineering, architecture and design, and is ranked among the first in the European Union according to the 2025 QS ranking. The university also serves as a technology development and transfer hub, with over 100 spin off companies and over 3000 patents. Within Horizon Europe, it has obtained funding for over 150M€ in over 300 projects, including 36 ERC grants.

The HEAP laboratory of the Department of Electronics, Informatics and Bioengineering is a cross-disciplinary research team of around 20 people with skills covering Embedded and Cyber Physical Systems, Design Methodologies, Low-power Design of Software and Hardware, Compiler Construction, and Embedded Systems Security and Data Privacy.

The group has been active for over two decades in designing architectures and in developing methodologies and prototype tools to support the automation of different design phases of advanced embedded and computing systems.

The summer period has been an important time for the ISOLDE project, marked by key milestones and fruitful exchanges across Europe.

In early July, representatives of our Work Package Leaders attended the official project review meeting in Brussels. This review was a significant moment to reflect on the progress made so far, showcase the results achieved, and receive constructive feedback from the EC reviewers. We are proud to share that the outcome was very positive, confirming that ISOLDE is on the right track to deliver on its ambitious objectives. The reviewers also provided valuable recommendations, which will help us shape our next steps with even greater precision and impact.

Later in the month, members of the consortium came together in Munich for an in-person meeting. This gathering offered the perfect setting to discuss in detail the future work plan, align our strategies with the recommendations from the review, and strengthen our collaborative spirit. The agenda combined technical discussions with opportunities for open exchange, fostering both focused work and creative thinking.

Our time in Munich was not only about work — we also took the chance to organise a social programme, allowing team members to connect beyond the meeting room. These moments of informal interaction help reinforce the trust, understanding, and shared commitment that underpin the success of the project.

An additional highlight of the Munich meeting was a joint workshop with four sister projects: TRISTAN, REBECCA, RIGOLETTO, and Scale4Edge. This collaborative session was designed to learn more about each project’s goals, approaches, and progress, while identifying potential synergies and areas for alliance. Such cross-project exchanges are essential for building a strong research and innovation ecosystem, ensuring that efforts complement rather than duplicate each other, and opening the door to new opportunities for cooperation.

The combination of a successful project review, a productive consortium meeting, and a great workshop with related initiatives made July a month of momentum for ISOLDE. With renewed energy and clear direction, we look forward to implementing the next phase of our work.

The European Union continues to play a pivotal role in accelerating the RISC-V ecosystem. Projects like TRISTAN and ISOLDE are driving innovation, collaboration, and open hardware development across Europe.

Florian Wohlrab, CEO of OpenHW Foundation & RISC-V Ambassador, explored how these initiatives are shaping the future: https://hubs.la/Q03Ck5pD0

The gap between design and implementation is a bottleneck in hardware development. With Register-Transfer Level (RTL) generation often neglecting the physical implementation constraints tapeouts can delayed or even broken. As RTL-models – sometimes already called RTL-programs – are said to be the way for technology independent digital designs this challenge is often despised. Even more, re-use of RTL-IPs is claimed to be the way to close the digital design gap, that is the disparity between the growth of manufacturable transistors and the ability to design circuits and systems that effectively utilize them.

However, as the physical reality is ignored the re-use rate is lower than planned. When digging deeper, following four major reasons can be identified. First, different features and feature variants of an IP are needed to fully cover the potential of re-use and to avoid modifications in code that is claimed to be re-usable. Examples include the number of channels in communication-IPs or timer-IPs, the sizes of objects used for holding addresses or data, or slight variations in implementation. Second, the soft-IP must operate in different domains and under different conditions. Therefore, it is required to provide special features, e.g., safety, security, or (self-) test features. Third, even though RTL code can conceptually be synthesized to any semiconductor target technology, some code items in the RTL code such as instantiating clock gates, memories, or pads remain technology-specific. Further, meeting timing constraints may partially require to implement functionalities differently. Last but not least – and fourth - FPGA prototypes are increasingly used for validation purposes, making it essential to ensure the seamless mapping of RTL code to both ASIC and FPGA technologies.

All these challenges require the RTL code to follow different and sometimes partially contradicting requirements. One approach to tackle these challenges is making use of so-called generic IPs that can be configured with generics (VHDL) or parameters (SystemVerilog). However, generic-IPs can support different object sizes but do not provide features like optional ports or flexibility in instantiating components. To enhance adaptability, generator-based approaches have been developed that leverage partly hardware generation languages (HGL). VHDL and SystemVerilog configurations conceptually can (re-)configure component instantiations but this feature is not supported by synthesis tools.

As the HDL and HGL approaches cover the mentioned challenges only to some extent the Model-Driven Architecture (MDA)-based code generation, an iterative flow of model refinements and final un-parsing, is the way of choice to generate RTL and other collaterals in a highly reusable way. With the MDA inherent transformation and generator approach, RTL code can be provided in a significantly more flexible manner, supporting facets such as feature dependent ports or port properties. In addition, MDA promotes the idea of creating abstract models that describe system functionality, which can then be automatically or semi-automatically transformed into RTL code. This approach is appealing due to its promises of efficiency, reusability, and reduced human error. From a high-level perspective, re-use of code is replaced by re-using transformation and generation utilities.

The picture on the left gives an overview on the process. Generation that starts with a Computation Independent Model (CIM). We call this model Model of Things (MoT) as only things, their attributes and relations are defined. This model is translated in a Platform Independent (Implementation) Model, which we call Model of Design (MoD) as it includes already most of the design aspects. With a transformation, the MoD is migrated to a MoD’ which is still platform independent put easier to translate to the target platform. The target platform specific code is finally reached by translating to a Platform Specific Model (PSM), which we call Model of View as it closely relates to the target formalism. The MoV is finally unparsed to the target code. As hardware platforms are inherently heterogeneous and often optimized for specific use cases, platform awareness is an essential requirement for getting the best results. For example, the priority for a CPU-centric SoC would be high clock speeds and general-purpose processing. For FPGA platforms, however, parallelism and reconfigurability are keys. Defining and considering metrics such as timing constraints, resource availability, and power considerations, highly influence the power, performance, and area (PPA) attributes of a design.

PAF, the Platform Aware Flow, is a systematic platform-model (PM)-based approach aimed at unlocking the full potential of MDA based RTL generation by enhancing the platform awareness while preserving the abstraction advantages. The approach leverages a Platform Model (PM) to improve the overall chip design flow by enabling the generation of platform-aware RTL, along with platform-specific constraints and directives whilst keeping the generator well structured. These enhancements guide backend tools to achieve better quality results, facilitate faster design closure, and incorporate testing and safety features tailored to the target platform. This approach bridges the gap between RTL and implementation through increasing automation. It also ensures that the resulting chips meet testability and safety requirements.

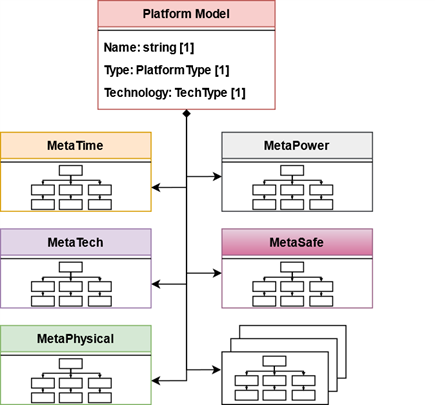

A sketch of a Platform Model is shown on the left. It is composed of aspect specific sub-models besides platform descriptive attributes. These sub-models steer the PIM-to-PIM’ and PIM’-to-PSM transformations. Each of that covers other aspects as timing and power, technology specific components or safety specific properties.

The key to the PAF-approach is to introduce platform models as conceptually foreseen by the MDA vision. Second pillar is a flexible engine that interprets platform models and modifies design models through a set of fundamental editing operations, resulting in RTL code that is tailored for the target platform. We further utilize the platform models together with the design model to generate other collaterals. We have demonstrated the effectiveness of our approach through qualitative analysis and quantitative results, ultimately showing a significant 73% reduction in code generation effort for industrial-grade designs. By bridging the gap between design and implementation, our Platform-Aware RTL Generation flow has the potential to revolutionize the hardware development process as well as enabling faster time-to-market, improved design quality, and reduced development costs.