The automotive domain has witnessed a remarkable transformation in recent years, primarily driven by the pervasive integration of embedded systems. These specialized computer systems are the linchpin of modern vehicles, revolutionizing their performance, safety, and efficiency. In the context of motor control scenarios, the adoption of the RISC-V architecture stands out as a significant milestone. RISC-V, an open and extensible instruction set architecture (ISA), has gained prominence for its adaptability, modularity, and flexibility. It offers an innovative approach to addressing the intricate requirements of motor control in the automotive industry.

One significant extension of the RISC-V architecture for motor control is the incorporation of a vector accelerator unit (VAU). These VAUs provide the ability to execute parallel processing operations more efficiently, which is highly advantageous in motor control applications. By leveraging vector accelerator units, embedded systems can achieve improved computational performance and optimize energy consumption. The extension of RISC-V with VAUs empowers embedded systems to handle the intricate mathematics and algorithms required for motor control, contributing to improved performance and reduced energy consumption.

The aim to further optimize the RISC-V embedded architecture for the automotive domain is closely connected with the utilization of Power, Performance, and Area (PPA) analysis, as it turns out to be a crucial factor on the way to the deployment of an efficient solution. PPA analysis offers a comprehensive evaluation of the system's power efficiency, computational performance, and hardware area utilization. This analytical approach aids in fine-tuning the embedded system's architecture to strike an optimal balance between these critical parameters. By leveraging PPA analysis, engineers can design embedded systems that meet the stringent requirements of motor control while minimizing power consumption and overall hardware footprint.

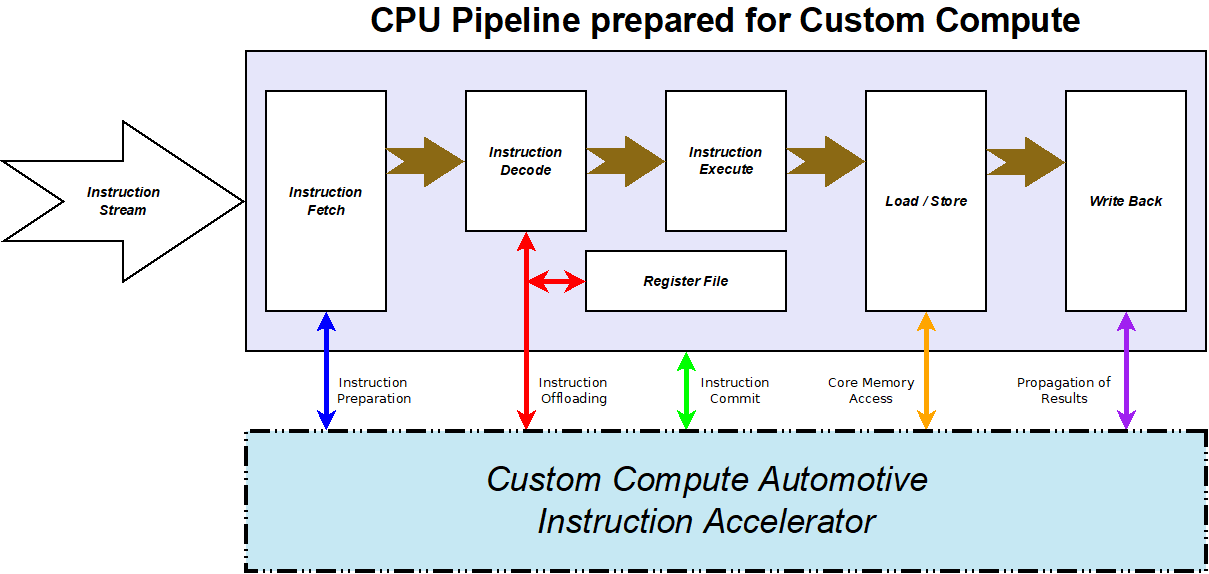

The role of the ISOLDE project team from Brno University of Technology (BUT) from Czech Republic aims at the PPA optimization possibilities of a custom compute automotive instruction accelerator with vector processing capabilities, which represents an extension of RISC-V based target architecture developed in a close collaboration with the Codasip company (another Czech partner of the ISOLDE project). Obviously, the partnership between an academic institution and commercial company will be leveraged in that context.

The intended way of PPA optimization is two-fold. First, profiling of the processor setup (RISC-V core and accelerator unit) will be performed in Codasip Studio development tool with a special attention given to the Instruction Set Architecture (ISA) regarding:

Then, further optimization steps can be taken on so called Register Transfer Level (RTL) representation of the target embedded architecture. The capability of Codasip Studio to produce SystemVerilog representation of the whole hardware setup plays an important role here. Such kind of hardware description can be analyzed using Synopsys toolset, e.g. Design Compiler and RTL Architect, together with the help of ASIC technology libraries. Such an approach allows to refine the target architecture on a near-physical level with accurate power estimation, timing constraints and estimation of the floor area needed.

The advantages of this integrated approach accompanied by thorough PPA analysis and optimization steps are multifaceted. First, the adoption of RISC-V architecture with VAUs significantly enhances the processing power, enabling sophisticated control algorithms and real-time responses for motor control applications. Second, the extensibility and modularity of RISC-V make it adaptable to evolving motor control standards and requirements, facilitating future-proof designs. Lastly, PPA analysis-driven optimizations ensure that the embedded systems strike an optimal balance between performance, energy efficiency, and hardware utilization, thereby contributing to sustainable and reliable automotive solutions.

Links

Brno University of Technology (BUT) – https://www.fit.vutbr.cz

Development toolset by Codasip – https://codasip.com/products/codasip-studio/

Logic synthesis tools by Synopsys - https://www.synopsys.com/implementation-and-signoff/rtl-synthesis-test.html

Images